실리콘 vafers의 크기는 당신이 생각하는 것이 아니며, 불가능한 작은 칩 “3nm”및 “2nm”에 대해 듣고 있습니까? 측정보다 마케팅 마크입니다.

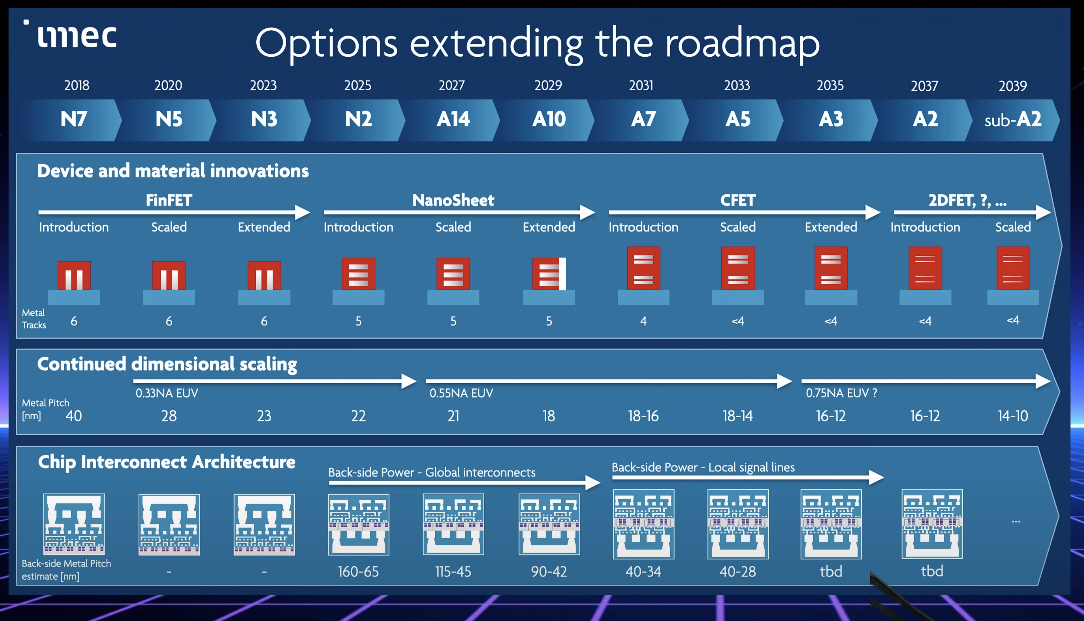

YouTuber Techtechpotato가 최근에 발생한 Interunersity (IMEC) 마이크로 전자 공학 센터의 최신 예측은 현재 TSMC 레인 레인과 0.2 MM을 생성 할 것으로 예상되는 A14 (1NM) 칩이 포함 된 인텔 Lienerry 18A 및 14A 프로세스 기술 기술뿐만 아니라 현재 TSMC 레인 레인을 대표합니다 (AT10 (AT10 2039).

실제로,이 숫자는 칩으로의 물리적, 측정 가능한 트랜지스터와는 다르며, 우리는 심지어 10nm 장벽을 깨뜨리기 전에 2030 년대 말까지 기다려야 할 수도 있습니다. 이유는 다음과 같습니다.

실리콘 와플은 2nm의 크기를 생각하기 위해 작지 않습니다.

TSMC 및 Intel의 개발 중 1.8 nm의 현재 2 나노 미터 및 실리콘 기술은 2nm 두께 인 와플에서 만들어지지 않습니다.

2nm은 또한 수지의 두 트랜지스터 사이의 거리가 아닙니다.

칩 제조업체는 생산 중 웨이퍼 표면에서 달성 할 수있는 기능의 최소 크기에 따라 실리콘 와플과 관련이있는 경향이 있습니다. 현재이 크기는 일반적으로 말합니다 이름 칩의 물리적 특성보다는 절차 노드.

실제로, 대략 1997 년, 실리콘 절차 노드의 이름이 잘못되었습니다. 인텔의 250 nm 프로세스 노드는 실제로 도어 길이가 200 nm입니다. 인텔은 2011 년까지는이 절차를 계속해서 과소 평가했습니다. 2011 년까지는 실질적인 절차 노드가 22 nm로 떨어졌으며 실제 길이의 도어 길이는 26 nm입니다.

TSMC와 Samsung은 2018 년 7NM 노드를 사용하여 실리콘의 “마케팅 인식”을 받아 들였는데, 이는 10 nm의 인텔 실리콘을 향한 도어 길이와 유사했습니다.

그리고 거기의 혼란은 나선형 만 계속되었습니다.

그러나 현재 3 나노 미터의 현재 칩에 대한 단단한 물리적 측정 크기를 찾고 있다면 도어 길이는 16-18 nm이고 금속 경사면은 약 23nm입니다.

따라서 현재 대화 2nm 및 3nm에 관계없이, 우리는 IMEC의 의도 된 Sub-A2 칩셋 2039의 세대가되는 한 10 나노 미터의 “진정한”실리콘을 보지 못할 것입니다.

Wafe와 Moore의 법칙의 크기는 함께 진행됩니다.

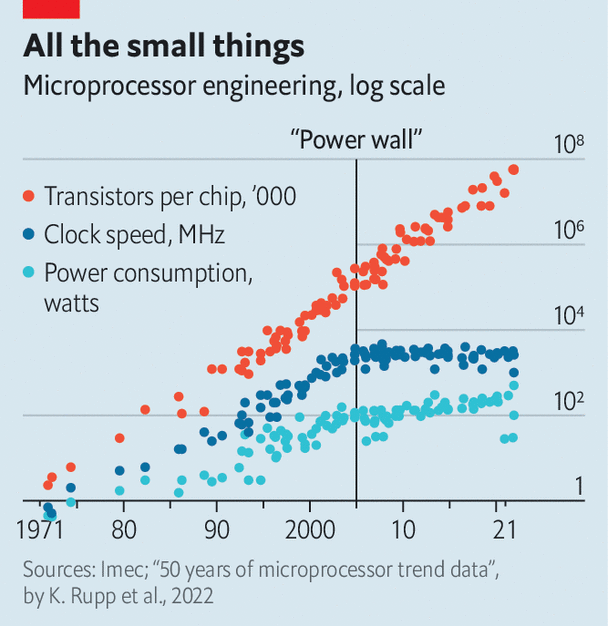

간단한 새로 고침으로 Moore의 법칙은 마이크로 칩 설계에서 관찰되며 약 2 년 동안 통합 원에 트랜지스터 트랜지스터의 수를 설정합니다. 실리콘 리인터가 더 작기 때문에 트랜지스터가 너무 증가하지만 결국 모든 것이 물리 법칙을 숭배해야합니다.

그의 이름과는 반대로 무어의 법칙은 실제 법이 아니라 마이크로 칩 디자인에서 관찰합니다. 결국, 반도체는 원의 따뜻함이 실제 설계 문제가되기 전에 너무 작아 질 수 있습니다.

NVIDIA 전무 이사 Jensen Huang은 개별 그래픽 카드의 열 제한이 높기 때문에 Moore 법률 경향을 크게 유지한다는 생각에 반대하는 반면, CPU와 같은 Intel Chipset Lunar Lake는 성장을위한 공간이 더 많습니다 (또는 감소).

그러나이 알림 IMEC가 실리콘 수지의 올바른 크기와 건축 및 트랜지스터 기술 칩의 예상 개선에 대한 IMEC를 통해 무어의 법칙은 비현실적인 것과는 거리가 멀다. 트렌드가 지난 10 년 동안 계속 될지 여부는 안전하게 말할 수 없지만 현재의 예측에 따라 달성됩니다.

따라서, 하위 A2 (10NM LG) 칩셋의 잠재적 인 트랜지스터 수가 놀랍습니다. 현재 Intel Core Ultra 9 285K는 약 180 억 개의 트랜지스터를 보유하고 있으며, 이는 2039 년에 A2 칩셋이 약 3 천억 개의 트랜지스터를 가질 수 있음을 의미합니다.