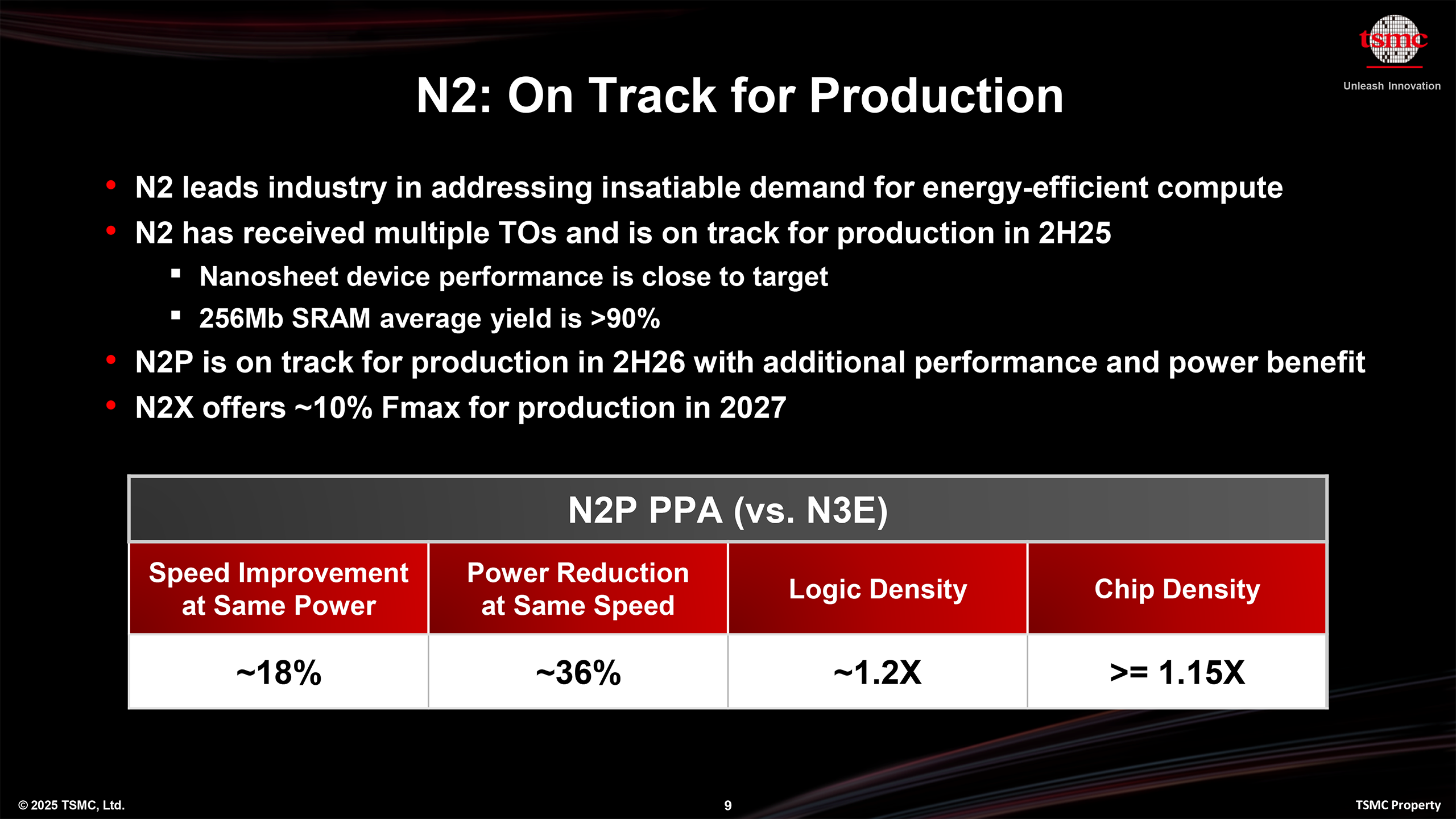

TSMC는 올해 말 N2 (2Nm) 프로세스 기술에 대한 칩을 만들기 시작하기 때문에 N2 Wafers 가격의 소문과 다음 노드의 가격이 나타났습니다. 우리는 TSMC가 N2 기술을 사용하여 Rezina 당 최대 30,000 달러를 청구 할 계획이라는 것을 이미 알고 있었지만, 현재 대만에 본사를 둔 China Times는 회사가 A16 Node (1.6NM)에 의해 표시되는 ‘고급 노드’에 대해 수지 당 최대 45,000 달러를 청구 할 것이라고보고했습니다.

2nm 생산은 비싸다

“2nm 칩에 대한 TSMC 파운드리의 가격은 Rezin 당 30,000 달러로 증가했습니다. [more] 중국 타임즈 (China Times)는이 성명서는 TSMC 소문 N2 NOD보다 45% 높다고 보도했다.

다른 계약자에게 TSMC의 가격에 대해 알아야 할 몇 가지 사항이 있습니다. 첫째, 파운드리의 가격은 생산량과 고객에 크게 의존합니다.

애플은 가장 큰 구매자가 가장 진보 된 TSMC 프로세스 기술이며 업계의 동료보다 적은 비용을 지불합니다. AMD, Intel, Nvidia 및 Qualcomm과 같은 다른 클라이언트와 관련하여 가격은 고객의 주요 노드 섭취 섭취를 기반으로 해당 볼륨의 비율을 제외하고는 총 수량에 따라 다릅니다.

따라서 등록 된 모든 인용문은 TSMC (또는 Foundry) vaphones에 관한 것이며 가장 근사치입니다. TSMC가 가격과 양에 대해 언급하지 않는다고 말할 수는 없습니다. 따라서 유일한 비교 지점은 다른 비공식 가격입니다.

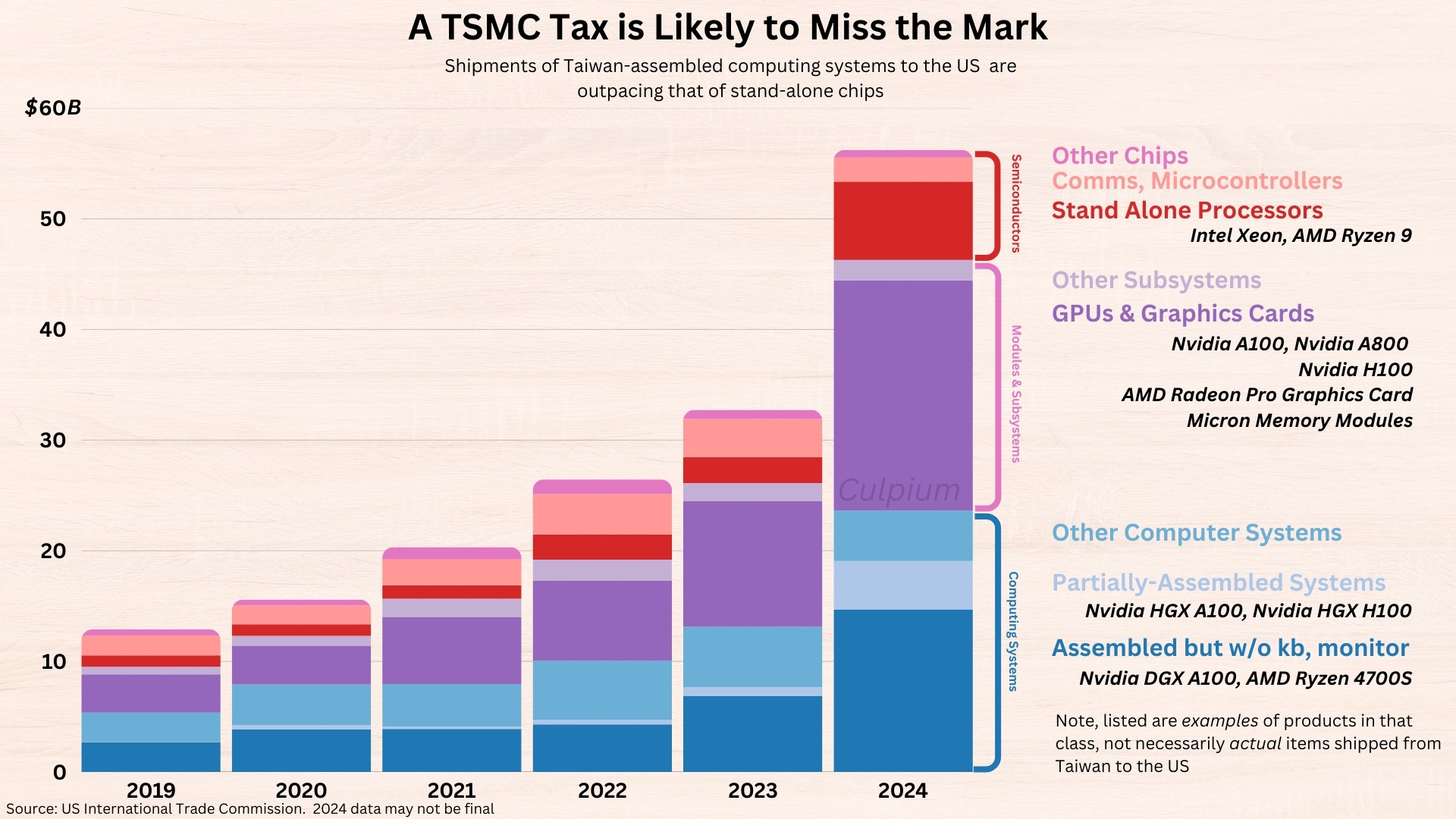

|

매듭 |

공보 가격 |

년도 |

|---|---|---|

|

A16 |

$ 45,000 |

2026 H2 |

|

n2 |

$ 30,000 |

2025 H2 |

|

n3 |

18,000-20,000 달러 |

2022 H2 |

|

N5 |

$ 16,000 |

2020 |

|

N7 |

$ 10,000 |

2018 |

|

N10 |

$ 6,000 |

2016 |

|

n28 |

$ 3000 |

2014 |

|

40nm |

$ 2,600 |

2008 |

|

90nm |

$ 2,000 |

2004 |

몇몇 주요 칩 개발자는 2NM 기술로 이동합니다. AMD는 최근 코덴지 (Codenji) 이름 베니스 (Venice)와 후지츠 (Fujitsu)에 의해 차세대 epyc 서버를위한 최초의 실리콘을 생산했음을 확인했다. 이 보고서는 Mediatek이 TSMC의 N2 매듭의 칩 (SOC)의 새로운 세대 모바일 시스템에 대한 설계 작업을 완료해야한다고 밝혔다. Qualcomm은 또한 같은 노드에서 Snapdragon 8 Elite 모바일 플랫폼의 3 세대를 개발했다고한다.

애플은 N2가 처음으로 채택 할 것으로 예상되지만 회사는 공식적으로 확인하지 않았다. 이 경우 A20 시리즈 차세대 프로세서와 M6 시리즈의 프로세서는 N2 매듭에 의존 할 것으로 예상되지만, 교육을받은 추측입니다.

TSMC는 올해 후반에 N2에 기반을 둔 칩 생산을 동시에 동시에 두 팹으로 증가시킬 것입니다. 이는 전례없는 이벤트입니다 (나중에 자세히 설명). 이 보고서는 2nm의 TSMC 내부 목표는 올해 말까지 약 30,000 개의 와플의 월간 생산 능력을 나타냅니다.

Waffe를 돌리고 가격으로 달려?

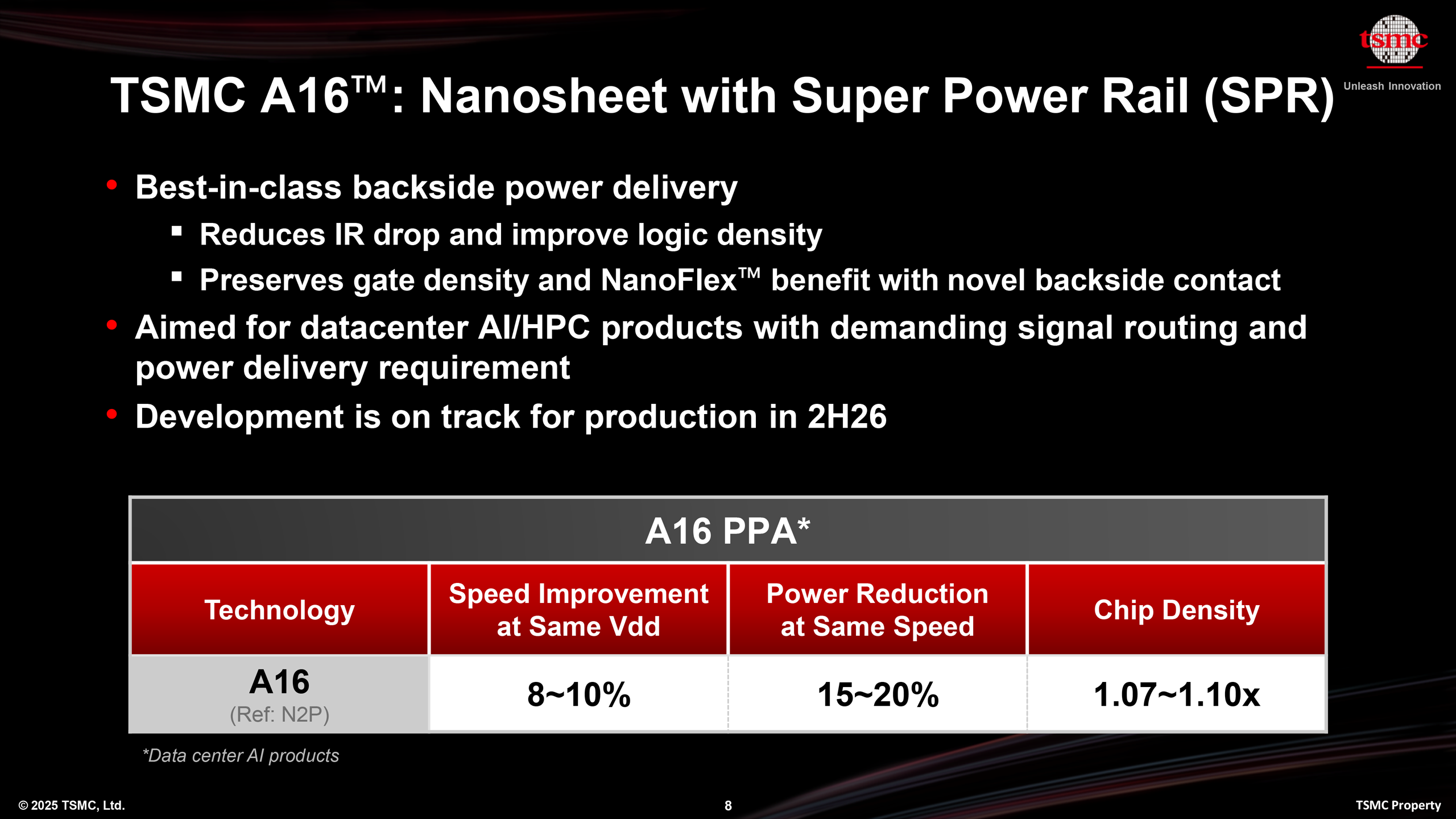

N2 Rezin 당 30,000 달러의 가격은 많이 보이지만 “더 진보 된”매듭의 경우 $ 45,000는 약간 참을 수없는 것처럼 보입니다. 이 보고서는 특히 A16 프로세스 기술을 언급하지는 않지만 가격 A14 이상의 고급 생산 노드에 대해 논의하기에는 너무 이르기 때문에이 보고서는 TSMC 클래스 1,6NM 기술을 사용하여 처리 된 Vafers의 가격을 나타낼 가능성이 높습니다.

소금 한 덩어리와 함께 $ 45,000의 견적을 받아야합니다. 앞에서 언급했듯이 다른 고객은 다른 가격을 지불합니다. 그러나 우리는 여전히 A16 와플이 N2 동료보다 훨씬 비싸다는 소문이 여전히 추측 할 수 있습니다.

그 이유는 간단 할 수 있습니다. N2 및 N2P와 달리 A16은 전원 공급 장치 네트워크 (BSPDN)를 지원하며, 이는 AI 및 HPC 애플리케이션 감독 근처의 대규모 크기의 프로세서에 특히 유용하지만 상당히 비쌉니다.

BSPDN 생산에는 생산 공정에서 몇 가지 추가 단계가 필요하므로 가격에 큰 영향을 미칩니다.

첫째, 칩은 평소와 같이 계속됩니다. 트랜지스터는 증착, 리소그래피, 식사 및 도핑과 같은 전통적인 단계를 사용하여 실리콘 컷 앞에 구축되어 활성 장치를 형성합니다. 트랜지스터가 제작되면 Vafel은 하이브리드 바인딩 기술을 사용하여 빈 캐리어로 얼굴을 향하게됩니다.

그런 다음 원래의 vafel을 연삭 및 화학적 기계적 연마를 통해 뒤에서 조심스럽게 얇게하여 실리콘의 두께를 몇 마이크로 미터로 줄여 활성 트랜지스터 층의 바닥을 노출시킵니다.

뒷면이 노출되었으므로 새로운 금속 상호 연결은 전력을 전달하여 독점적으로 퇴적합니다. TSMC는 BSPDN의 가장 효과적인 구현을 사용하지만 생산하기가 가장 어렵습니다.

BSPDN은 두꺼운 구리 라인을 연결하여 트랜지스터로 직접 저항을 줄입니다. 뒷면에서 처리 한 후 Vafel은 표준 포장 단계를 거칩니다.

전력 및 배선 신호의 분리는 더 나은 전력 전달, 전압 방울 감소 및 더 빠른 신호 감소를 위해 전면을 방출하여 총 칩 성능을 향상시킵니다.

그러나 후방 전력 공급 비용은 다음 세대 및 HPC GPU AI와 같이 크고 비싼 프로세서를 개발하는 회사에 대한 사용을 제한 할 것이며, 이는 킬로와트 힘을 소비하고 BSPDN의 큰 이점을 얻을 것으로 예상됩니다.

극단적 인 개발 비용

이 보고서는 2NM 칩의 개발 비용이 약 7 억 7 천 5 백만 달러로 예상되며, 이는 소수의 회사 사용에 많은 제한이 있습니다. 그러나 캐치가 있습니다.

눈의 7 억 7 천 5 백만 달러의 이미지는 아마도이 특정 기술에 의존하고 더 많은 칩을 포함하는 전체 플랫폼의 개발에 관여 할 것입니다.

예를 들어, TSMC N3 프로세스 기술에 의존하는 Apple 제품 목록에는 현재 A17 Pro, A18, A18 Pro, M3, M3 Pro, M3 Max, M4, M4 Pro 및 M4 Max를 포함한 9 개의 제품이 포함됩니다. 결국,이 목록은 A19, A19 Pro, M5, M5 Pro 및 M5 Max로 확장 될 가능성이 높습니다.

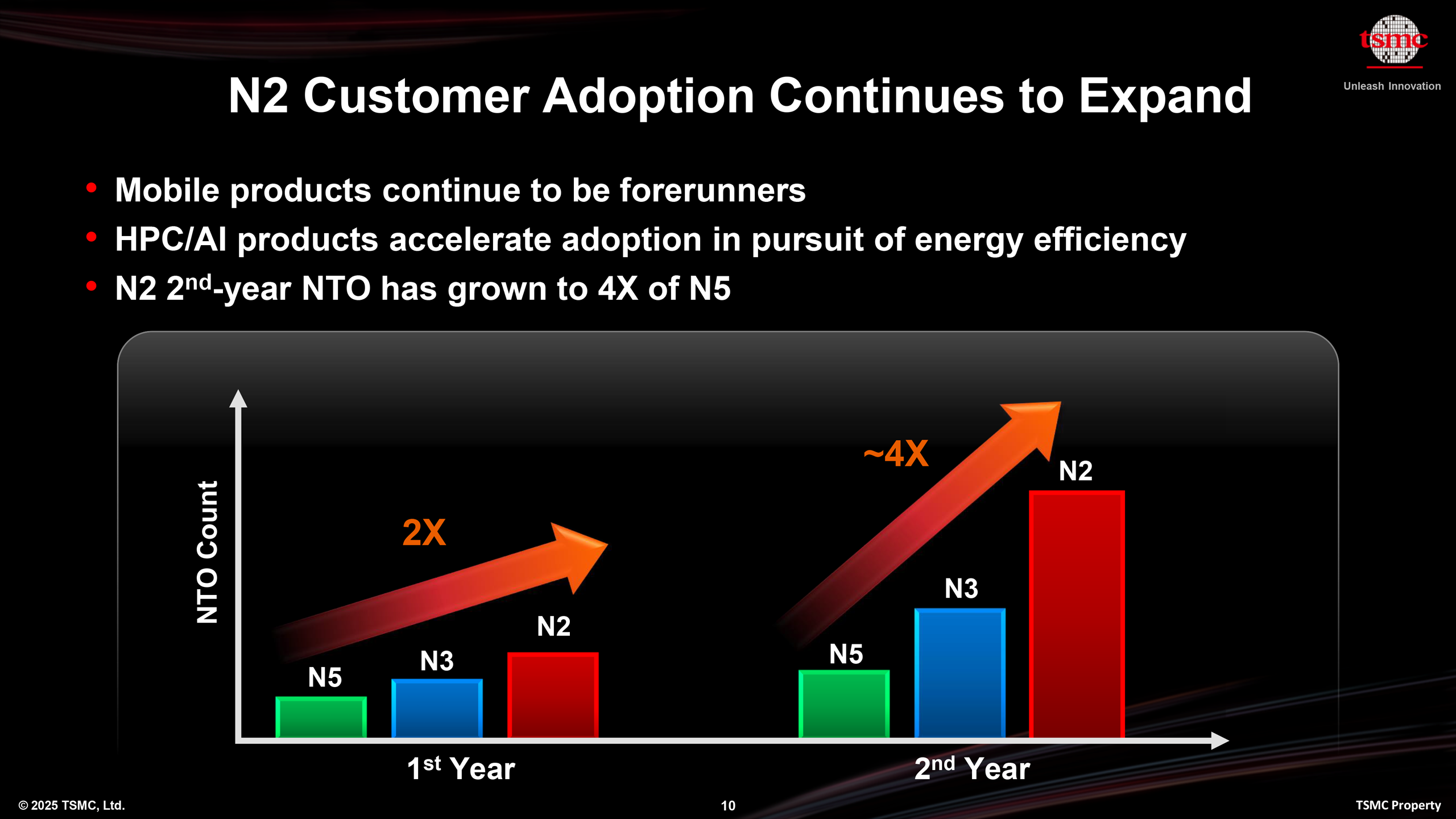

미리 극단적 인 비용에도 불구하고, 생산 2 년차에 새로운 카세트의 수는 N5와 유사한 단계에서 달성 된 것보다 4 배 더 높을 것으로 예상됩니다. 이 요소는 AI 칩, HPC, 클라이언트 컴퓨터 및 스마트 폰을 개발하는 여러 회사의 주요 노드의 중요성을 강조합니다.

TSMC는 프로세스 설계 (N2P, A16, N2X 등)를 위해 동일한 프로세스에서 N2 프로세스 기술 및 기타 노드에 대한 큰 수요를 충족시키기 위해 Hsinch 및 Kaohsiung에서 N2를 사용할 수있는 두 개의 제조 시설을 준비합니다. 결국 회사는 대만과 미국에서 N2를 사용할 수있는 추가 팹을 건설 할 것입니다.

업계의 관찰자들은이 매듭이 고객의 강렬한 관심으로 인해 기록 용량의 증가율을 달성 할 것으로 기대합니다. TSMC 자체는 미래의 소득을 창출하는 AI 가속기에 대해 낙관적이며 2024 년부터 시작하여 40%의 범위에 5 년의 성장률을 예측합니다.

따르다 Google 뉴스의 Tom의 하드웨어 우리의 피드에서 우리의 뉴스, 분석 및 리뷰를 얻기 위해. 다음 버튼을 클릭하십시오.