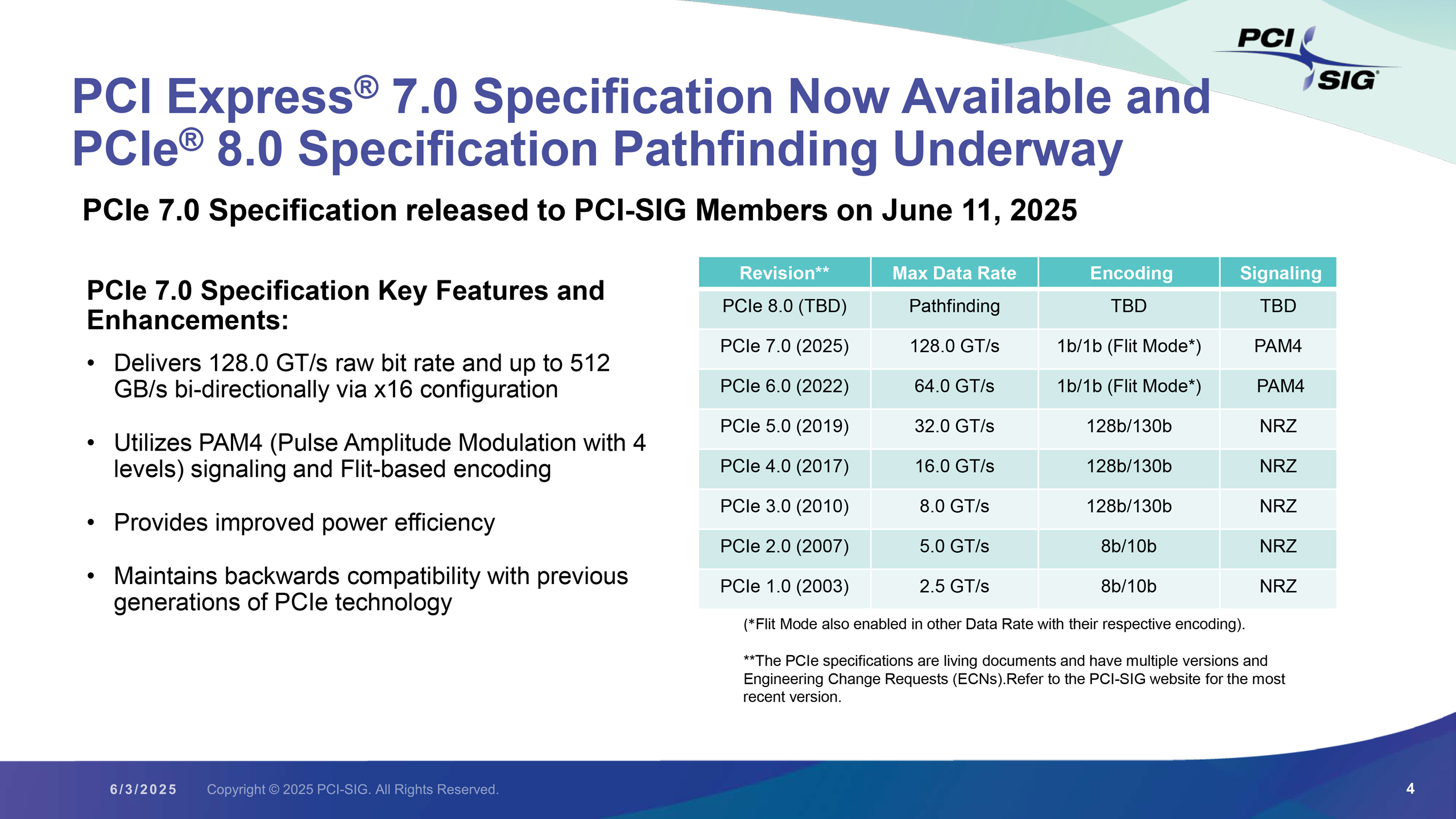

PCIE 사양의 개발을 감독하는 PCI-SIG는 수요일에 PCIE 7.0 사양을 완료하여 조직 구성원에게 전송했으며 기술 개발에 중요한 이정표가되었습니다. 이와 별도로이 회사는 PCIE 8.0의 승객 경로 인 2030 년 이외의 어딘가에 사용될 서로의 링크에 대한 사양 인 PCIE 7.0의 성능을 두 배로 늘리고 16 개 이상의 스트립을 2 방향으로 제공 할 수 있다고 말했다. 또한이 회사는 올해 PCIE 6.0 하드웨어 6에 대한 상호 운용 테스트를 시작할 계획을 반복했습니다.

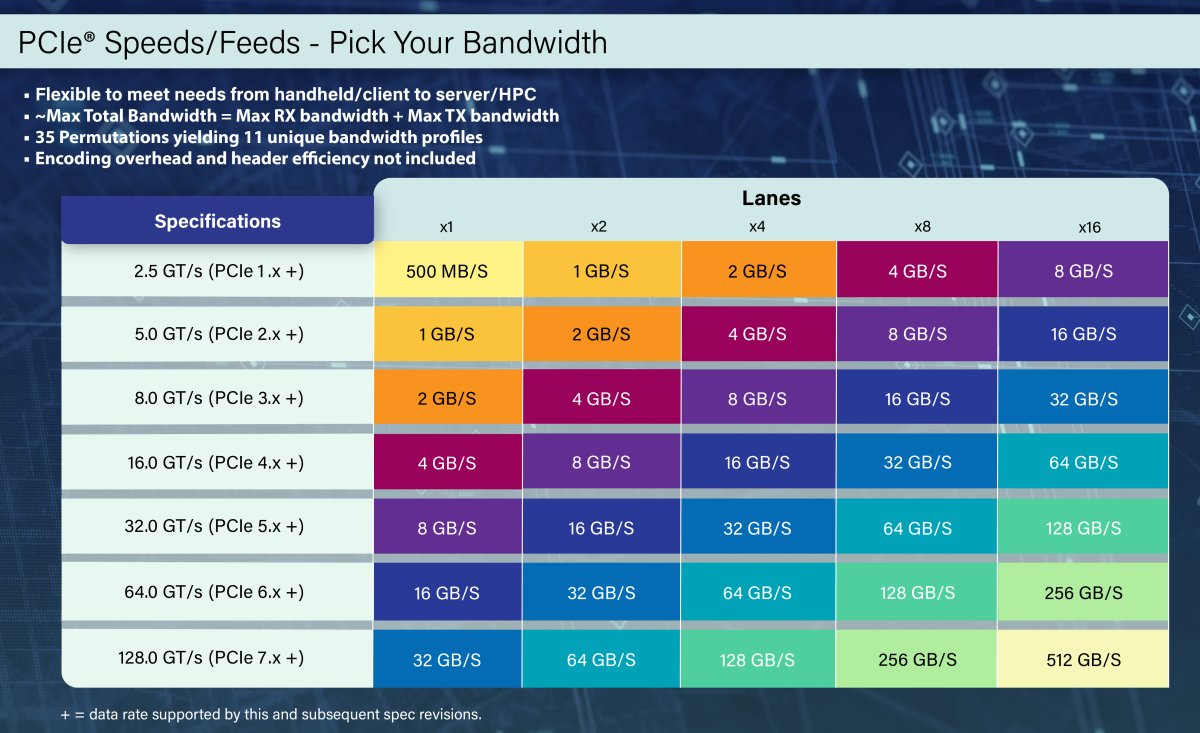

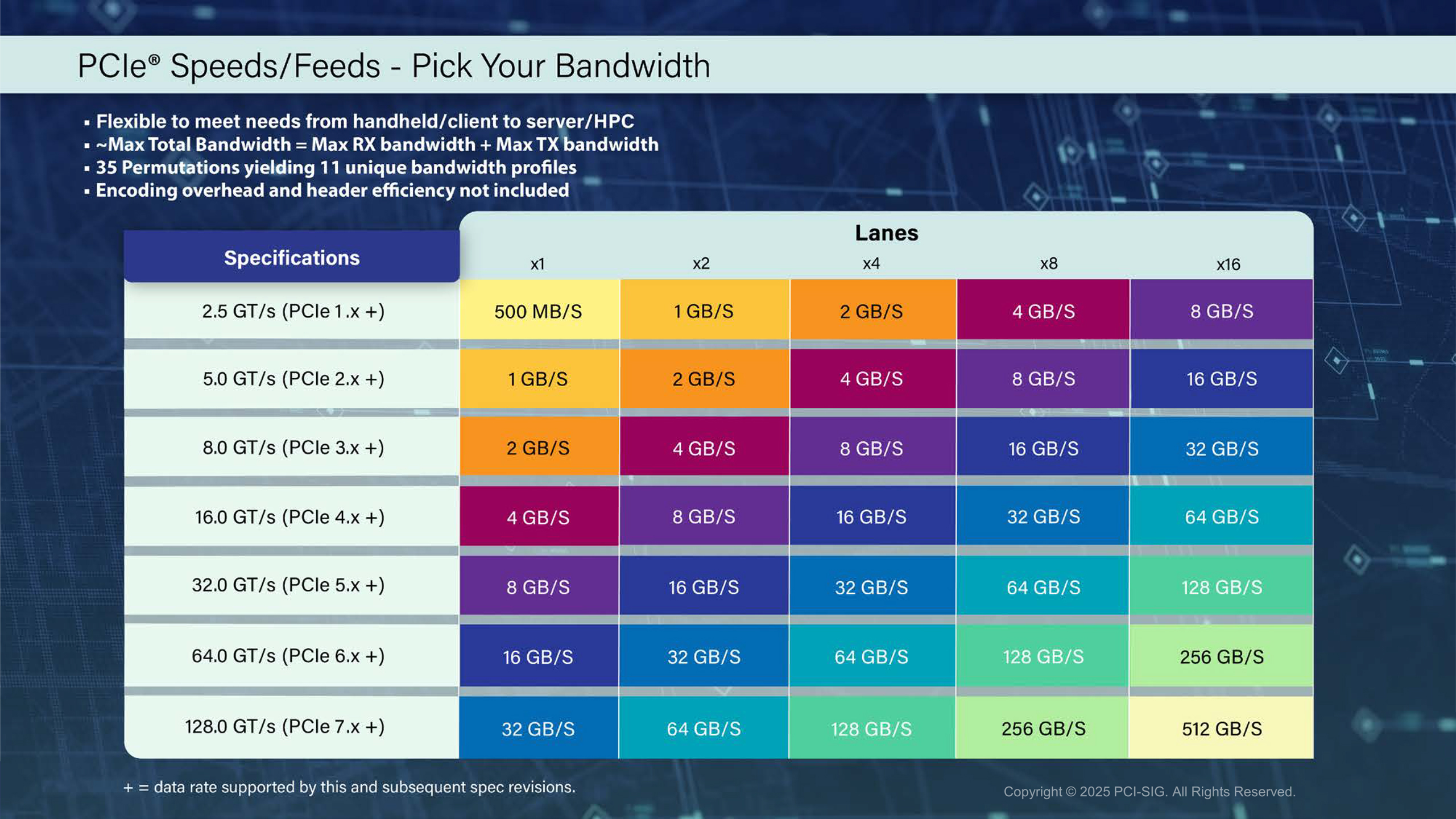

PCIE 8.0은 몇 년 동안 떨어져 있었지만 PCIE 7.0은 훨씬 더 가깝습니다. PCIE 7.0 사양은 테이프 당 데이터 전송 속도를 128 gt로 증가시킵니다. 각 방향은 PCIE 6.0 브래킷의 두 배나 빠르고 PCIE 5.0보다 4 배 빠릅니다. 이러한 성능이 크게 증가하면 16 PCIE 7.0 테이프가있는 장치는 각 방향으로 256GB/s로 전송할 수 있으며 프로토콜에 의존하지 않습니다. 인터페이스의 새로운 버전은 여전히 1B/1B FLIT의 코딩 방법의 유지 보수로 PM4 신호를 사용하며, 이는 PCIE 6.0에 처음 소개되었습니다.

128GT/s에서 데이터 전송 속도 PCIE 7.0의 속도를 달성하기 위해 PCIE 7.0 개발자는 신호의 물리적 비율을 32GHz 이상으로 증가시켜야했습니다. PCIE 5.0과 6.0은 16GHz 신호의 물리적 속도를 사용하여 NRZ 신호 전달 및 PM4 신호 전달 (심볼 당 2 비트를 허용)으로 32 gt/를 허용합니다. PCIE 7.0을 통해 개발자는 2017 년 이후 처음으로 물리적 주파수를 늘려야했으며, 이는 구리 와이어를 사용하는 장거리에서 32GHz 신호 무결성을 유지하는 것이 매우 어려운 일이기 때문에 다른 수준에서 큰 작업이 필요했습니다.

이 업데이트는 원시 투과성 외에도 더 길거나 더 복잡한 전기 채널에 대한 향상된 전력 효율과 더 강력한 지원을 제공합니다. 특히 케이블에 대한 솔루션에 사용될 때 800g 이더넷, 초경량 컴퓨팅과 같은 차세대 중심의 투과성 투과성의 요구를 충족시키기 위해 다른 것들.

아마도 PCI-SIG가 발표 한 가장 흥미로운 발표는 PCIE 8.0에 대한 발표가 발표되었으며, 조직 구성원은 적극적으로 가능성을 탐색하고 2030 이상을 사용할 수있는 표준의 가능성을 정의합니다. 흥미롭게도, PCI-SIG는 PCIE 8.0이 데이터 전송 속도를 256 gt로 두 배로 늘릴 것인지 (16 스트립을 사용하여 양방향 1 tb/) 너비의 폭을 256 gt로 두 배로 늘릴 것인지 물었다. 또한 PCI-SIG는 PCIE 8.0을 허용하기를 기대하고 있으며, 이는 구리 와이어를 통해 둘 이상의 성능에 연결될 것입니다.

“희망합시다 [to double performance]그러나 현재 나는 최종 주장을하고 싶지는 않지만 우리의 희망입니다. “Yanes는 기자 회견에서 말했습니다.” 우리는 광학이 유일한 방법이라고 생각하지 않습니다. 그러므로 우리는 전기적으로 일할 수 있기를 희망하고 생각하지만, 그곳에는 명확한 대답이 없습니다. 길은 방금 시작되었습니다. 그러니 우리에게 그것을 해결할 시간을주십시오. 그러나 우리는 우리가 전기적으로 일할 수 있다고 생각합니다. 우리는 그것이 광학 일뿐이라고 생각하지 않습니다. “

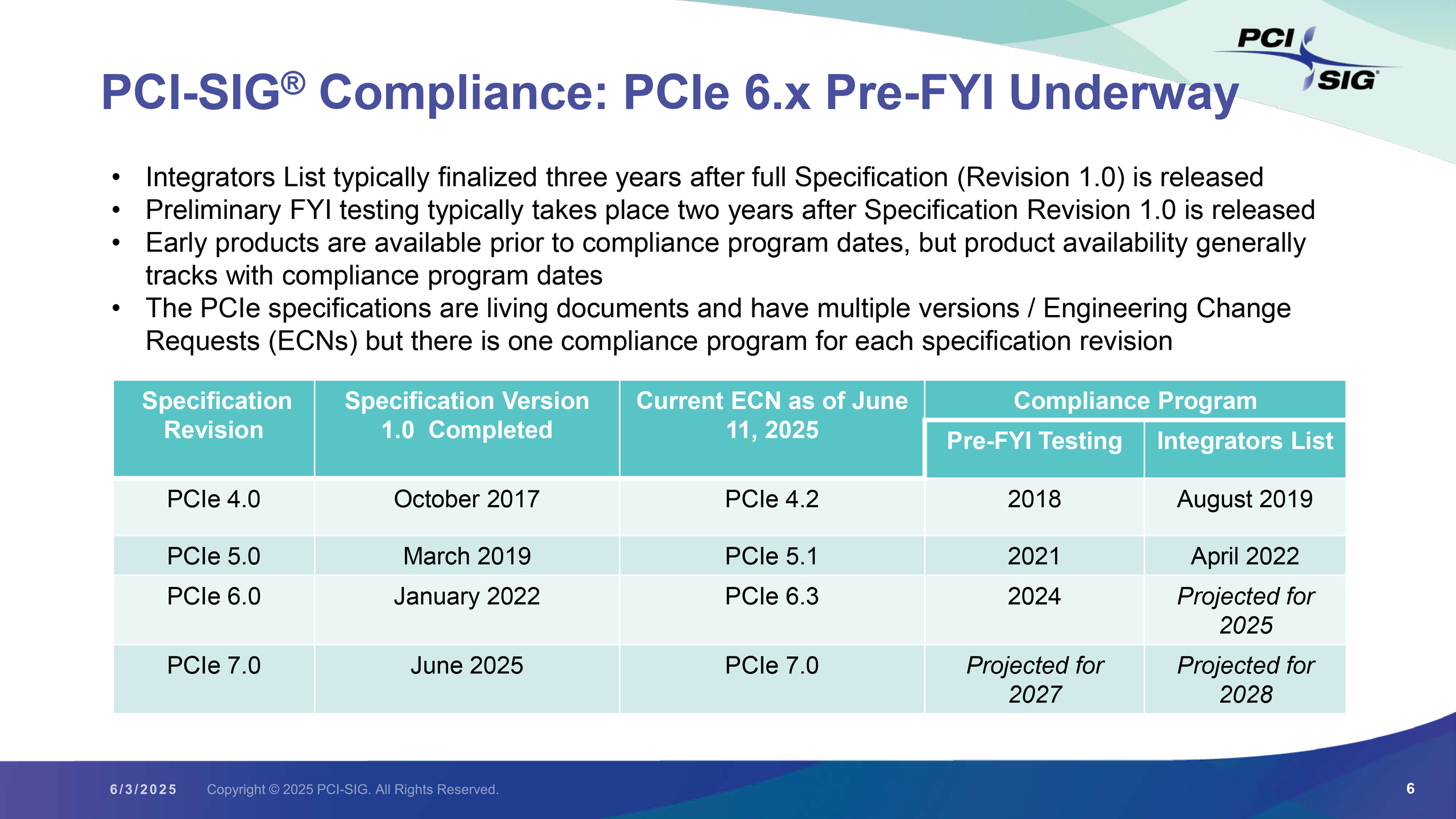

PCIE 7.0 표준 공식 게시를 통해 AMD, Intel 및 Nvidia를 포함한 PCI-SIG 회원은 PCIE 사양에서 지원하는 플랫폼 개발을 완료 할 수 있습니다. PCI-SIG는 2027 년에 예비 증언 테스트를 시작하고 2028 년에 예정된 공식 상호 운용성 테스트를 시작할 계획입니다. 따라서 모든 것이 계획대로 진행되면 2028 년에서 2029 년 사이에 시장에서 실제 PCIE 7.0 장치 및 플랫폼이 예상됩니다.

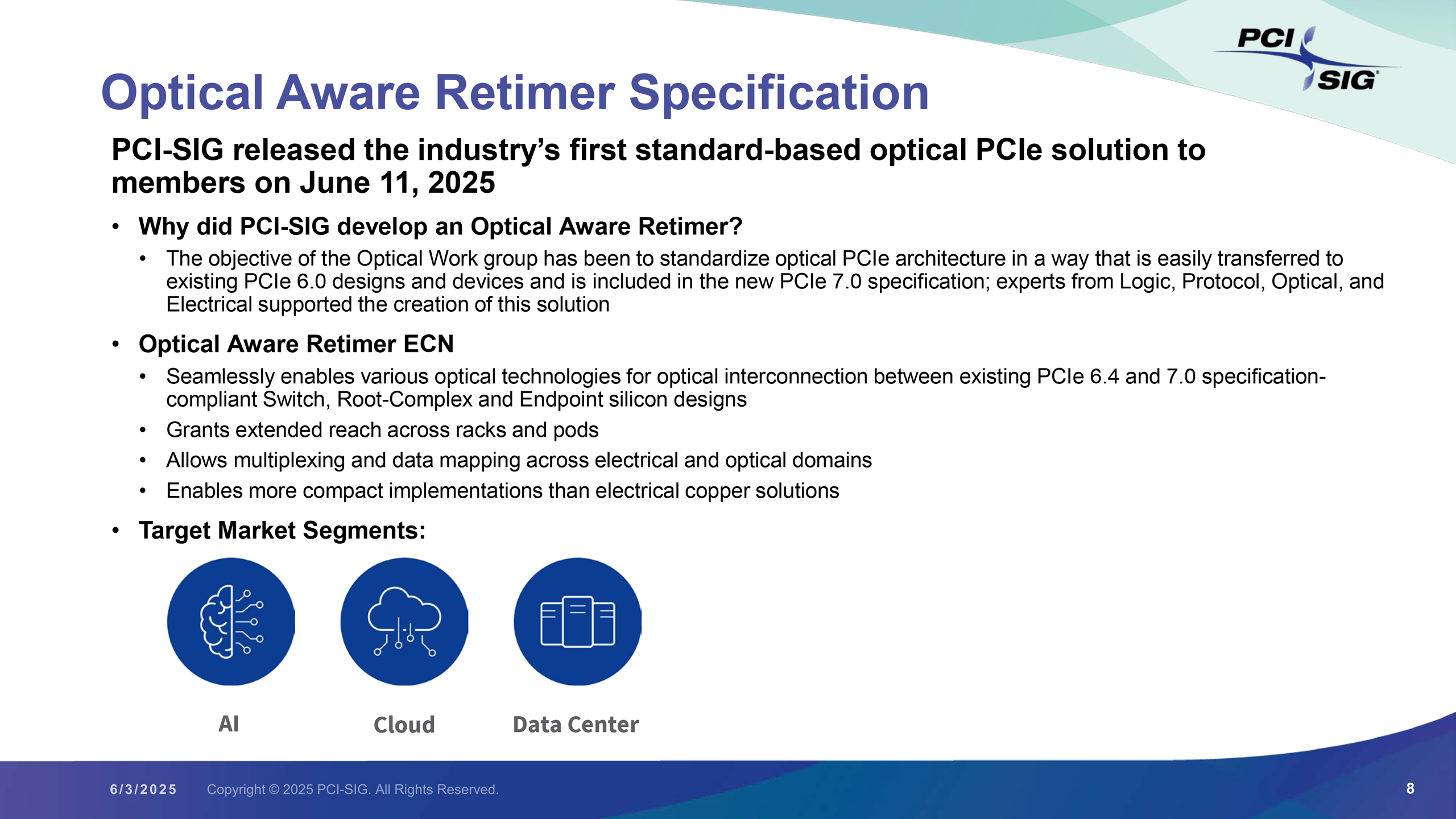

PCI-SIG는 PCIE 7.0 전환점을 발견하는 것 외에도 예상보다 약 1 년 후 2025 년 PCIE 6.0의 Hardware 6.0 Companion 목록 목록 목록을 공식적으로 출시 할 계획을 다시 강조했습니다. PCIE Gene6 전체에 대해 말하면, PCIE 6.4의 사양은 이제 PCIE 6.4와 PCIE 7.0 기기 사이의 광학 기술을 사용하는 산업 방법을 정의합니다. 그러나 광학 PCIE 타이에 대한 상호 운용성 테스트는 나중에 시작됩니다.

따르다 Google 뉴스의 Tom의 하드웨어 우리의 피드에서 우리의 뉴스, 분석 및 리뷰를 얻기 위해. 다음 버튼을 클릭하십시오.